# HiD2990P 倍频板原理

## 组成结构

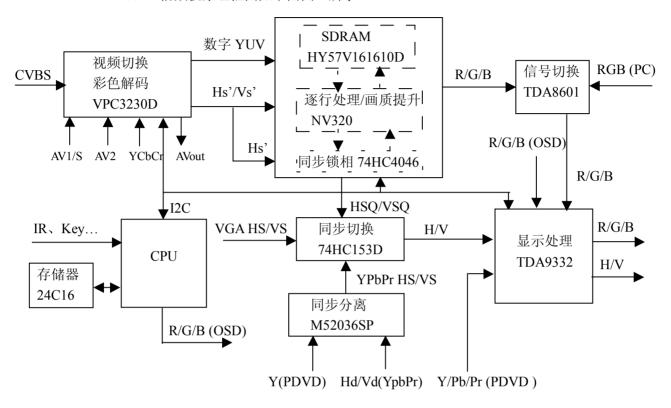

HiD2990P 倍频板原理框图如下面图 1 所示。

图 1: HiD2990P 倍频板原理框图

整个倍频板主要由视频解码、逐行转换、同步分离、显示处理、CPU 控制、信源切换等功能部分组成。(详细电路原理请参照 HiD2990P 线路图。)

视频解码功能由UN07(VPC3220D)来完成。VPC3230D是微科公司(MICRONAS)生产的梳状滤波视频处理器,该芯片内部集成了视频切换、Y/C分离(4H自适应梳状滤波器)、A/D转换、数字解码、PIP等功能。其功能强大,外围电路简单,有4路AV输入,其中一路带S端子,2路RGB/YPbPr输入,一路AV输出;PIP功能具有4种显示大小15种显示模式;视频解码输出支持ITU-R 601/656数字输出接口。该IC采用80脚PQFP封装,管脚功能如表1所示。

| 衣   | 表 T: VPC3220D官脚功能 |                 |           |    |  |  |  |  |

|-----|-------------------|-----------------|-----------|----|--|--|--|--|

| I/O | 符号                | 功能说明            | 电压值       | 引脚 |  |  |  |  |

| 输入  | B1/CB1IN          | B1 或 Cb1 模拟信号输入 | 0~3.5Vp-p | 1  |  |  |  |  |

|     | G1/Y1IN           | G1 或 Y1 模拟信号输入  |           | 2  |  |  |  |  |

|     | R1/CR1IN          | R1 或 Cr1 模拟信号输入 |           | 3  |  |  |  |  |

|     | B2/CB2IN          | B2 或 Cb2 模拟信号输入 |           | 4  |  |  |  |  |

|     | G2/Y2IN           | G2 或 Y2 模拟信号输入  |           | 5  |  |  |  |  |

|     | R2/CR2IN          | R2 或 Cr2 模拟信号输入 |           | 6  |  |  |  |  |

|     | ASGF              | 模拟信号接地          | 0V        | 7  |  |  |  |  |

|     | VGAV              | VGA 场同步输入(不用)   |           | 16 |  |  |  |  |

表1: VPC3220D管脚功能

|    | CIN       | S端子色度输入         | 0~3.5Vp-p | 71          |

|----|-----------|-----------------|-----------|-------------|

|    | VIN1      | 视频 1/S 端子亮度输入   | 0~3.5Vp-p | 72          |

|    | VIN2-VIN4 | 视频 2~视频 4 输入    | 0~3.5Vp-p | 73-75       |

|    | FB1IN     | RGB 快速削隐输入      | 1.0Vp-p   | 79          |

| 输出 | FFIE      | FIFO 输入允许(不用)   |           | 19          |

|    | FFWE      | FIFO 写控制(不用)    |           | 20          |

|    | FFRSTW    | FIFO 读写复位(不用)   |           | 21          |

|    | FFRE      | FIFO 读控制(不用)    |           | 22          |

|    | FFOE      | FIFO 输出允许(不用)   |           | 23          |

|    | CLK20     | 20.25 MHz时钟输出   | 3.3V CMOS | 24          |

|    | LLC2      | 倍频时钟输出          | 3.3V CMOS | 27          |

|    | LLC1      | 时钟输出            | 3.3V CMOS | 28          |

|    | Y0-Y7     | 8 位亮度数据输出       | 3.3V CMOS | 40-37,34-31 |

|    | C0-C7     | 8 位色度数据输出       | 3.3V CMOS | 50-47,44-41 |

|    | INTLC     | 隔行输出(不用)        |           | 53          |

|    | AVO       | 有效视频输出(不用)      |           | 54          |

|    | FSY/HC    | 前端同步/水平钳位脉冲(不用) |           | 55          |

|    | MSY/HS    | 主同步/行同步脉冲       | 3.3V CMOS | 56          |

|    | VS        | 场同步脉冲           | 3.3V CMOS | 57          |

|    | FPDAT     | 前端/后端数据(不用)     |           | 58          |

|    | CLK5      | CCU 5MHz 时钟输出   | 3.3V CMOS | 60          |

|    | VOUT      | 模拟视频输出          | 2.0Vp-p   | 70          |

| 控制 | SCL       | I2C 时钟          | 3.3V CMOS | 13          |

|    | SDA       | I2C 数据          | 3.3V CMOS | 14          |

|    | RESQ      | 复位输入,低电平有效      | 3.3V      | 15          |

|    | TEST      | 测试输入            | 0V        | 16          |

|    | YCOEQ     | Y/C 输出允许        | 0V        | 17          |

|    | I2CSEL    | I2C 地址选择        |           | 67          |

| 供电 | VSUPCAP   | 数字供电去耦电容        | 3.3V      | 9           |

|    | VSUPD     | 数字供电电压          | 3.3V      | 10          |

|    | GNDD      | 数字供电接地          | 0V        | 11          |

|    | GNDCAP    | 数字供电去耦电容接地      | 0V        | 12          |

|    | GNDPA     | 模拟引脚接地          | 0V        | 25          |

|    | VSUPPA    | 模拟引脚供电          | 3.3V      | 26          |

|    | VSUPLLC   | LLC 电路供电        | 3.3V      | 29          |

|    | GNDLLC    | LCC 电路接地        | 0V        | 30          |

|    | GNDY      | Y输出接地           | 0V        | 35          |

|    | VSUPY     | Y 输出供电          | 3.3V      | 36          |

|    | VSUPC     | C输出供电           | 3.3V      | 45          |

|    | GNDc      | C输出接地           | 0V        | 46          |

|    | GNDsy     | 同步信号接地          | 0V        | 51          |

|    | VSUPSY    | 同步信号供电          | 3.3V      | 52          |

|    | VSTBY     | 待机供电电源          | 3.3V      | 59          |

| ]  | ASGF      | 模拟区接地           | 0V        | 64          |

|    | GNDF   | 模拟前端接地        | 0V   | 65  |

|----|--------|---------------|------|-----|

|    | VRT    | 参考电压点         | 2.5V | 66  |

|    | ISGND  | 模拟输入信号接地      | 0V   | 68  |

|    | VSUPF  | 模拟前端供电        | 5V   | 69  |

|    | VSUPAI | 模拟前端器件供电      | 5V   | 76  |

|    | GNDAI  | 模拟前端器件接地      | 0V   | 77  |

|    | VREF   | 参考电压点         | 2.5V | 78  |

|    | AISGND | 模拟元件信号地       | 0V   | 80  |

| 其他 | XTAL1  | 20.25MHz 时钟输入 |      | 62  |

|    | XTAL2  | 20.25MHz 时钟输出 |      | 63  |

|    | NC     | 空脚            |      | 8,6 |

逐行转换功能由 UN02、UN04、UN08 和 UN09 等 IC 来实现。UN02 型号为 NV320,是 nDSP 公司生产的多功能视频图像增强处理芯片,NV320 内置的逐行转换处理器,可把 NTSC/PAL 制式的隔行信号转换为 SDTV 标准的 480P/60Hz 逐行格式,同时可提供彩色、亮度瞬态改善(CTI、LTI),动态黑电平扩展,动态运动自适应降噪等多种画质改善电路功能。UN04(74HC4046)为同步锁相环 PLL 集成电路,主要为 UN02 提供精确的同步信号。UN08 和 UN09(HY57V16161D)为 SDRAM 帧存贮芯片,为 UN02 提供容量为 1M x 32bit 的帧数据缓冲区。NV320 采用 208 脚 PQFP 封装,管脚功能请参照《技术专刊》,74HC4046 采用 16 脚 DIP 封装,管脚功能如表 2 所示。

表 2: 74HC4046 管脚功能

| 引脚 | 符号    | I/O | 功能说明        | 引脚 | 符号   | I/O | 功能说明       |

|----|-------|-----|-------------|----|------|-----|------------|

| 1  | PCP   | O   | 相位比较器脉冲输出   | 9  | VCIN | I   | VCO 输入     |

| 2  | PC1   | O   | 相位比较器1输出    | 10 | SF   | О   | 解调输出       |

| 3  | BIN   | I   | 比较器输入       | 11 | R1   | О   | 电阻 R1 连接点  |

| 4  | VCOUT | О   | VCO 输出      | 12 | R2   | О   | 电阻 R2 连接点  |

| 5  | INH   | I   | 禁止控制输入      | 13 | PC2  | О   | 相位比较器 2 输出 |

| 6  | CA    | O   | 电容 C1 连接点 A | 14 | AIN  | I   | 信号输入       |

| 7  | СВ    | O   | 电容 C1 连接点 B | 15 | ZEN  | О   | 相位比较器3输出   |

| 8  | GND   | P   | 接地          | 16 | VCC  | P   | 供电电源       |

同步分离由 UN10(M52036SP)来实现。M52036 是 MITSUBISHI 公司生产的同步信号处理芯片,可以自动地从三种不同方式存在的信号中分离出一种同步信号:分离的同步信号(双极性 1-5 $V_{P-P}$ )、复合同步信号(双极性 1-5 $V_{P-P}$ )、视频信号中的同步信号(负极性同步信号),并能对被选的这些同步信号进行波形处理,它最适合对自动寻址式显示器、监示器进行同步信号处理。M52036SP 集成电路采用 20 脚 SDIP 封装,其管脚功能如表 3 所示。

表 3: M52036SP 管脚功能表

| 引出脚 | 名称   | 引出脚电<br>压 | 引出脚功能说明                   |

|-----|------|-----------|---------------------------|

| 1   | 行同步信 | 直流 0V     | 行同步信号逻辑输出脚,该脚出现高电平、低电平或高  |

|     | 号状态  | 或 5.0V    | 电平与加到⑥脚的正极性,空载或负极性输入信号有关。 |

| 2  | <br>  场同步信号状态                  | 直流 0V 或 | 场同步信号逻辑输出脚,该脚出现高电平、低电平或高                               |  |  |  |

|----|--------------------------------|---------|--------------------------------------------------------|--|--|--|

| 2  | <b>奶</b> 門少信 5 <b>小</b> 恋      | 5.0V    | 电平与⑧脚输入信号的正极性、空载或负极性有关。                                |  |  |  |

|    | 绿基色信号分离                        | 开路时大    | 绿基色(视频)分离滤波脚,外接电阻、电容组成滤波                               |  |  |  |

| 3  | 电路的基极滤波                        | 约为 4.0V | 时间常数,放电型电阻可以改善自偏电路响应,低的电                               |  |  |  |

|    | 电路                             |         | 阻值会减小自偏电路增益。                                           |  |  |  |

| 4  | 绿基色信号输入                        | 开路时大    | 视频信号中同步信号的绿基色输入脚,用电容 C 连接绿                             |  |  |  |

|    | +文 114                         | 约为 4.0V | 基色信号,同步信号负极性。                                          |  |  |  |

| 5  | 接地                             | 0V      | 接地                                                     |  |  |  |

| 6  | 复合同步信号/行                       | 开路时大    | 复合同步信号或行同步信号输入脚,偏置约 6.0V,阻抗 10kΩ,整形与极性检测由内部接入的双向门限变换器实 |  |  |  |

| 0  | 同步信号输入                         | 约为 6.0V | 现,输入幅度 1.5V <sub>P-P</sub> 。                           |  |  |  |

|    |                                | 开咱时大    | 外接电容需要用作极性检测和无信号输入检测的滤波                                |  |  |  |

| 7  | 复合同步信号/行                       | 约为 6.0V | 器,电容越大,纹波越小,误动作也会减小,但检测响                               |  |  |  |

| ,  | 同步信号检测                         | (无信号)   | 应时间被加长。                                                |  |  |  |

|    |                                |         | 场同步输入脚,偏置约 6.0V,阻抗 10kΩ,整形与极性                          |  |  |  |

| 8  | 场同步输入                          | 开路时大    | 检测由内部接入的双向门限变换器实现,输入幅度                                 |  |  |  |

|    |                                | 约为 6.0V | 1.5V <sub>P-P°</sub>                                   |  |  |  |

|    | 场同步信号检测                        | 开路时大    | 外接电容需要用作极性检测和无信号输入检测的滤波                                |  |  |  |

| 9  |                                | 约为 6.0V | 器,电容越大,纹波越小,误动作也会减小,但检测响                               |  |  |  |

|    |                                | (无信号)   | 应时间被加长。                                                |  |  |  |

| 10 | <br>  场同步/分离调整                 | 开路时大    | 场同步分离调整引出脚,如无外接调整,门限值近似为                               |  |  |  |

| 10 | */J1997/J1994E                 | 约为 1.0V | 1.0V                                                   |  |  |  |

| 11 | <br>  场同步/分离输入                 |         | 场同步分离输入脚。复合同步信号由外部合成,因此,                               |  |  |  |

|    |                                |         | 复合同步信号进入场同步分离。                                         |  |  |  |

| 12 | 数字地                            | 0V      | 接地                                                     |  |  |  |

| 13 | V <sub>D</sub> <sup>+</sup> 输出 |         | 正极性场激励脉冲输出脚,为开路集电极输出型,该脚                               |  |  |  |

|    |                                |         | 可以调整输出幅度,充电电流大约为 6mA。                                  |  |  |  |

| 14 | V <sub>D</sub> <sup>+</sup> 输出 |         | 正极性行激励脉冲输出脚,为开路集电极输出型,该脚可以调整输出幅度,充电电流大约为6mA。           |  |  |  |

|    |                                |         | 负极性行激励脉冲输出脚,为开路集电极输出型,该脚                               |  |  |  |

| 15 | V <sub>D</sub> <sup>-</sup> 输出 |         | 可以调整输出幅度,充电电流大约为 6mA。                                  |  |  |  |

| 16 | Vec                            | 12.0V   | 电源电压                                                   |  |  |  |

|    |                                |         | 钳位脉冲输出脚,为开路集电极输出型,该脚可以调整                               |  |  |  |

| 17 | 钳位脉冲输出                         |         | 输出幅度,充电电流大约为 6mA。                                      |  |  |  |

| 10 | 行同步信号极性                        | 直流 0V 或 | 行同步信号逻辑输出脚,低电平、低电平或高电平的出                               |  |  |  |

| 18 |                                | 5.V     | 现与⑥脚输入信号正极性、无信号或负极性相对应。                                |  |  |  |

| 19 | 场同步信号极性                        | 直流 0V 或 | 场同步信号逻辑输出脚,低电平、低电平或高电平的出                               |  |  |  |

| 19 |                                | 5.0V    | 现与⑧脚输入信号正极性、无信号、负极性相对应。                                |  |  |  |

| 20 | 钳位时序                           |         | 钳位脉冲时序引出脚,钳位脉冲宽度与外接电阻、电容                               |  |  |  |

| 20 | MH 177H 1/1.                   |         | 有关、电阻、电容越大,则钳位脉冲宽度越宽。                                  |  |  |  |

显示处理功能由 UN01(TDA9332)来实现,TDA9332 是 PHILIPS 公司推出的 I2C 总 线控制显示处理芯片。其功能齐全,全总线控制,暗平衡自动控制,两路 RGB 输入,一路 YUV 输入,一路 RGB 输出,内部有 YUV—RGB 转换矩阵,行场幅度及中心、平行四

边形、枕形、梯形、四角、弓形等几何失真全部可总线调整。可用于单频(50Hz/60Hz)或倍频(100Hz/120Hz)扫描显示系统。其采用 44 脚 QFP 封装,单一 8V 供电电压,管脚功能如表 4 所示。

CPU 控制功能部分由 UN11 和 UN12 实现。UN11 采用东芝公司专为 TV 系统开发的 8 位 TV 控制专用微处理器 TMP88PS38N(OTP 版本),其内置 64KB 程序 ROM,2KB 数字 RAM,内置 OSD 字符发生器支持 384 个不同字符,可同时在屏幕上显示 32 列 x 12 行字符,菜单动画设计,三色半透明显示格式。TMP88PS38N 采用 42 脚 SDIP 封装,其相应管脚功能如表 5 所示。UN12(24C16)是容量为 16Kbit 的记忆 IC,存储各种配置、调整、频道等数据。

表 5: CPU 管脚功能

| 10.5 | 表 5: CPU 自脚功能 |     |                |    |       |     |                |  |  |

|------|---------------|-----|----------------|----|-------|-----|----------------|--|--|

| 引    | 符号            | I/O | 功能说明           | 引  | 符号    | I/O | 功能说明           |  |  |

| 脚    |               |     |                | 脚  |       |     |                |  |  |

| 1    | VSS           | _   | 接地             | 22 | OSD R | О   | 屏显红基色信号输出      |  |  |

| 2    | ROTATE        | О   | 旋转 PWM 输出      | 23 | OSD G | О   | 屏显绿基色信号输出      |  |  |

| 3    | SOUNDBOX      | О   | 外置音箱控制开关       | 24 | OSD B | О   | 屏显蓝基色信号输出      |  |  |

| 4    | POWERCUT      | О   | 音响状态关掉行输出      | 25 | OSD Y | О   | 屏显挖空信号输出       |  |  |

| 5    | AT            | О   | 音响信号输出         | 26 | FBP   | I   | 逆程反馈脉冲输入       |  |  |

| 6    | SYS1          | О   | 伴音制式控制         | 27 | VFB   | I   | 场反馈脉冲输入        |  |  |

| 7    | SYS2          | О   | 伴音制式控制         | 28 | DVDD  | I   | 电源             |  |  |

| 8    | SAW SW        | О   | 伴音制式控制         | 29 | DVSS  |     | 接地             |  |  |

| 9    | RSOUT         | О   | 开机复位 UN02 UN07 | 30 | TEST  |     |                |  |  |

| 10   | BUSOFF        | I/O | 总线关闭开关(未用)     | 31 | XIN   | I   | 晶振输入           |  |  |

| 11   | SCL           | I/O | I2C 总线时钟信号线    | 32 | XOUT  | О   | 晶振输出           |  |  |

| 12   | SDA           | I/O | I2C 总线数据信号线    | 33 | RESET | I   | 复位信号输入         |  |  |

| 13   | VGA-HS        | I/O | VGA 行频自动检测     | 34 | TV/PC | О   | TV 与 PC 信号切换输出 |  |  |

| 14   | AFT           | I   | 自动频率控制输入       | 35 | IR    | I   | 遥控接收输入         |  |  |

| 15   | KEY0          | I   | 按键控制输入         | 36 | VM    | О   | VM 控制开关输出      |  |  |

| 16   | KEY1          | I   | 按键控制输入         | 37 | CLK   | I/O | 与寄存器相连时钟       |  |  |

| 17   | WMUTE         | О   | 重低音静音控制开关      | 38 | DATA  | I/O | 与寄存器相连数据       |  |  |

| 18   | R/LMUTE       | О   | 主声道静音控制开关      | 39 | VVSS  |     | 接地             |  |  |

| 19   | WEBTV         | I/O | 网络电视控制开关       | 40 | YpbPr | О   | PDVD 信号选择开关    |  |  |

| 20   | STB           | О   | 待机信号输出         | 41 |       | I/O |                |  |  |

| 21   | I             | О   | 屏显菜单字输出信号      | 42 | VDD   | I   | 电源             |  |  |

信源切换功能由 UN03 和 UN06 组成,其中 UN3 型号为 74HC153,是双 4 选 1 数据选择器,用于同步信号的切换。UN06 为双通道 RGB 选择开关,在这里主要作为 VGA 信号及电视信号的切换选择。

## 线路原理

整个倍频板的信号输入输出主要通过 5 个插座与外部连接。其中 JN01 和 JN02 用于与 主板信号的连接, JN03 用于连接 CRT 板, JN04 用于连接 AV 板, JN05 用于连接 VGA 接口板。

#### 1、视频解码

从主板上过来的各种格式视频信号主要通过 JN02 插座输入倍频板。其中主板高频头 输出的复合视频信号 TV IN,通过 JN02 的 17 脚进入倍频板,经 CN189、190(220pF)、 LN21 (4.7uH) 低通滤波及 RN91 (75Ω) 阻抗匹配后, 经 CN118 (680nF) 耦合进 UN07 的 75 脚(VIN4)。从主板过来的 AV2 视频信号 VIDEO2 从 JN02 的 7 脚进入倍频板, 经 CN116 (680nF) 耦合进 UN07 的 73 脚 (VIN2)。从主板过来的 AV1 视频信号或 S 端子 Y 信号 SVIDEOY/V1 从 JN02 的 5 脚进入倍频板, 经 CN115 (680nF) 耦合进 UN07 的 72 脚 (VIN1)。主板过来的 S 端子 C 信号 SVIDEO-C 从 JN02 的 3 脚进入倍频板, 经 CN114 (680nF)耦合进 UN07 的 72 脚(VIN1)。从主板过来的隔行色差端子信号 YCbCr Y、YCbCr Cb 和 YCbCr Cr 分别从 JN02 的 11 脚、13 脚和 15 脚进入倍频板, 经阻抗匹配及低通滤波 后,分别由 CN138、CN133 和 CN140 (220nF) 耦合进 UN06 的 2 脚 (Y1)、1 脚 (CB1) 和 3 脚 (CR1)。UN07 在 CPU 的控制下选择相应的信号源送入 AD 转换器进行数字转换, 对于复合视频信号和 S 端子,将会被送入数字梳状滤波器进行 YC 分离,然后在进行视频 解码,解出亮度 Y 信号和两个色差信号 Cr 和 Cb。这三个信号以及 1 脚、2 脚和 3 脚过来 的信号都被送入一个混合器,经相应处理后的三路色差分量信号 Y、Cr 和 Cb 送入一个 2D 缩放控制单元,经过 PIP、对比度、亮度及峰化等处理后送入输出格式处理单元,然后从 40~37 脚、34~31 脚、50~47 脚和 44~41 脚输出 16 位 YUV 数字视频格式信号, 分别送入 UN02的171~176脚、178~179脚和189~196脚。

UN07 的 62 脚和 63 脚之间接 20.25MHz 的晶振,时钟同步信号和行场同步信号由 VPC3230D 内部产生。由 27 脚、56 脚和 57 脚输出到 UN02 的 24 脚、199 脚和 198 脚,为信号的逐行处理提供同步信号。28 脚的时钟信号通过 RN112 加到 UN02 的 24 脚。15 脚复位端与 UN02 的 204 脚相连,共同连接 CPU 的复位脚,以便开机正常工作后 UN07、UN02 进行复位。13 脚和 14 脚的 I2C 总线连接 VCP3230D 与 CPU 之间的通讯,以完成信号切换、制式转换等操作程序。

## 2、逐行处理

逐行处理及画质提升是通过 UN02 来完成的。UN02 采用 nDSP 公司 NV320P 的升级版本芯片 NV320,它具有更完善的功能及更简单的外围电路。UN04 同步锁相环 PLL 的集成电路为 UN02 提供精确的同步信号,它的 3 脚输入从 UN07 的 56 脚输出的行同步信号 HS3,14 脚接从 UN02 内部产生的同步信号 HRC(203 脚),两个信号经 UN04 内部的鉴相比较器比较,鉴相误差信号从 UN04 的 4 脚输出加到 UN02 的 202 脚,控制调整其压控振荡器的振荡频率,使其与 UN07 的频率相同。UN02 对输入的数字视频信号进行画质提升及逐行转换处理,完成 50Hz 隔行到 60Hz 逐行的扫描变换。UN08 和 UN09 是两个帧存贮器,为 UN02 逐行/隔行时提供帧数据缓存。经逐行变换处理后的数字视频 YUV 信号,在 UN02 内部通过矩阵转换成三路 RGB 信号,然后由内部精度为 10bit 的 D/A 转换转换器进行数模转换,完成数字信号到模拟信号之间的转换,处理完的 60Hz 逐行模拟图像信号 RGB 分别从 UN02 的 69 脚、56 脚和 63 脚输出,连接到 UN06 的 2 脚、3 脚和 4 脚。倍行后的行场同步信号从 38 脚和 41 脚输出,连接到 UN06 的 3 脚和 13 脚。

UN02 的 34、35 脚为 I2C 总线控制信号,与 CPU 之间传递隔行转换逐行过程中所需 的程序控制数据和时钟。UN02 的 32 位数字信号 DQ0~DQ31 和 11 位地址信号 A0~A10 分别连接 UN08 和 UN09 帧缓冲存储器的数据线及地址线,22 脚(CLK)、128 脚(CS)、129 (RAS)、135 (CAS) 和 136 (WE) 分别同时连接 UN08 和 UN09 的 35 脚(MEMCLK)、18 脚(CS)、17 脚(RAS)、16 脚(CAS) 和 15 脚(WE),UN02 的 21 脚(DQM0) 和 137 脚(DQM1) 分别连接 UN08 和 UN09 的 36 脚(UDQM)。

## 3、PDVD 分量信号处理

PDVD 信号从 JN05 输入。从 JN05 的 2 脚输入的 Y 分量信号 YPbPr Y, 一路经 QN17 射随输出到 UN10 的 4 脚进行同步分离。PDVD 的行场同步信号 YPbPr H 和 YPbPr V 从 JN05 的 7 脚和 8 脚输入,分别加到 UN10 的 6 脚和 8 脚。UN10 为 DTV 行场同步分离 IC, 且优先选择从 6 脚、8 脚输入的外加行、场同步信号。分离出的行场同步信号从 UN10 的 14 脚和 13 脚输出,连接到 UN03 的 6 脚和 10 脚。从 JN04 的 7 脚和 8 脚过来的行场同步信号 VGA Hs 和 VGA Vs 分别连接到 UN03 的 3 脚和 13 脚。UN02 的 38 脚和 41 脚输出得倍频后的 TV 行场同步信号 HSQ 和 VSQ 分别连接到 UN03 的 5 脚和 11 脚。这些同步信号由 UN03 进行切换后,从 UN03 的 7 脚和 9 脚输出,送入到 UN01 的 24 脚和 23 脚处理。

PDVD Y 信号另一路经 QN08、QN09 放大,由高频提升网络 CN44、CN45、CN46、LN05 高频提升后,经耦合电容 CN163 送入 UN01 的 28 脚。从 JN05 的 4 脚、6 脚输入的色差分量信号 YPbPr Pb、YPbPr Pr,分别经 QN11、QN13 反向放大,高频提升后耦合到 UN01 的 27 脚、26 脚,此时输入的 Y/Pb/Pr 比例为 1:-1.33:-1.05 (TDA9332 芯片要求)。

### 4、PC 信号处理

从 JN04 插座的 1、3 和 5 脚输入的 VGA RGB 信号经 RN176、RN177、RN178、CN166、CN177、CN177 直接耦合到 UN06 的 6 脚、7 脚和 8 脚,与加到 2 脚、3 脚和 4 脚的逐行电视信号 RGB 进行切换,从 12 脚、11 脚和 10 脚输出的 RGB 信号经电阻 RN38、RN31、RN39,电容 CN154、CN155 和 CN156 低通滤波后,由 CN18、CN19、CN20 耦合进显示处理芯片 UN01 的 30 脚、31 脚和 32 脚。UN06 的 5 脚为信号控制端,与 CPU 的 34 脚相连,高电平时选择 PC VGA 输入信号,低电平时选择 TV 电视信号。

#### 5、显示处理部分

由 UN06 选择的逐行电视 RGB 基色信号或 VGA RGB 基色信号分别从 UN06 的 12 脚、11 脚和 10 脚输出,从 UN01 的 30 脚、31 脚和 32 脚输入;经过幅度处理后的逐行 DVD 分量 YUV 信号从 UN01 的 28 脚、27 脚和 26 脚输入,CPU 40 脚输出的 PDVD 选择信号从 UN01 的 33

脚输入; CPU 22 脚、23 脚、24 脚和 25 脚输出的三基色 OSD RGB 信号和 OSD 挖空信号分别 从 UN01 的 35 脚、36 脚、37 脚和 38 脚输入; 经 UN03 选择的行场同步信号从 7 脚和 8 脚输出, 从 UN01 的 24 脚和 23 脚输入。

UN01 在 CPU 的控制下对输入的 YUV 信号和 RGB 信号进行选择,经饱和度、色差和基色矩阵、对比度、亮度、白峰限幅、束电流控制、暗平衡调节和阴极束电流控制等一系列处理后,从 40 脚、41 脚和 42 脚输出 RGB 三基色信号。RGB 三基色信号经 QN04、QQN05、QN06 射随后连接到 JN03 的 9 脚、7 脚和 5 脚,由排线连接到 CRT 板 P502 的 5 脚、7 脚和 9 脚,从 CRT 板反馈回来的暗电流信号从 JN03 插座的 3 脚(BCK)输入,经电阻、电容及二极管保护滤波电路后,从 UN01 的 44 脚(BLKIN)输入。UN01 的 8 脚为行驱动脉冲信号输出,连接到 JN02 的 21 脚; UN01 的 1、2 脚为差分场锯齿波信号输出,连接到 JN02 的 27、29 脚。UN01 的 3 脚为东西枕校 E-W 信号输出端,连接 JN02 的 33 脚; UN01 的 4 脚为阳极高压检测输入,连接 JN02 的 35 脚; UN01 的 13 脚为行反馈脉冲输入端,连接 JN02 的 25 脚; UN01 的 43 脚为束流检测输入,连接 JN02 的 23 脚。UN01 的 10、11 脚为 12C 总线控制信号,连接 CPU 的 I2C 总线接口。

### 6、CPU 功能控制

UN11 为 CPU 控制芯片, 其除了对倍频板的功能控制外, 主板、CRT 板、音效板等功能也由 UN11 控制。

其中,JN02的11脚(VM)为速度调制功能控制端,连接UN11的36脚,用于控制CRT板上的速度调制功能。JN02的31脚(VFB)为场逆程输入端,连接UN11脚,主要用于OSD字符显示垂直方向的定位。

JN01的1脚(STB)为待机控制信号输出端,连接UN11的20脚,用于控制TV的待机工作状态。JN01的4脚(STB)为待机控制信号输出端,连接UN11的20脚,用于控制TV的待机工作状态。JN01的6脚(SYS1)、8脚(SYS2)和10脚(SAWSW)为伴音制式控制端,连接UN11的6脚、7脚和8脚,用于选择主板上二合一高频头的伴音制式。JN01的12脚(AFT)为AFT信号输入端,连接UN11的14脚,用于选合时频率的检测。JN01的12脚(AFT)为旋转功能PWM波形输出端,连接UN11的2脚。JN01的18脚(BUSOFF)、19脚(SDA)和20脚(SCL)为12C总线控制线,连接UN11的10脚、12脚和11脚。JN01的24脚(AT)为音响状态控制端,连接UN11的5脚。JN01的26脚(RSOUT)为复位控制输出端,连接UN11的9脚,用于控制UN02和UN07开机时复位。JN01的28脚(VMUTE)和30脚(R/LMUTE)分别为重低音和主声道静音控制端,连接UN11的17脚和18脚,用于控制功放的静音状态。JN01的32脚(IR)为红外遥控信号输入端,连接UN11的35脚。JN01的34脚(KEY0)和36脚(KEY1为按键输入端,连接UN11的15脚和16脚。