### 8M67 8M70 机芯维修手册

### 警 告

本手册仅供有经验的维修人员使用,不适用于一般消费者,手册中没有对非技术人员企图维修本产品而存在的潜在危害提出警告或提醒。电器产品应由有经验的专业技术人员进行维护和修理,任何其它人企图对本手册涉及的产品进行维护和修理将有可能受到严重伤害甚至有生命危险。

## 1 产品综述

#### 1.1 机芯概述

本机芯采用 MSTAR 公司的高集成芯片 MST6148,是一颗功能强大的超级单芯片,采用 Linux 操作系统。采用符合公司标准的 PCB 制板,可配多种新标准结构机型; 硬件系统由主板、电源板(或外加恒流板)、MEMC 模块板(配高清、120HZ 的液晶屏含有此模块)、卡拉 OK 接口板、接收板、指示灯板和键控板(感光模块包含在键控板中)组成; 可以支持 1366\*768 和 1920\*1080 的液晶屏。

#### 1.2 机芯概述

本机芯具有多种信号接口,功能配置如下:

- A. 1 路模拟电视信号输入, 1 路视频输入, 1 路分量输入, 3 路 HDMI 输入, 1 路 VGA 输入;

- B. 1路网络接口, 4路 USB 接口, 两路麦克风输入;

- C. 3 路音频输入: 1 路视频的, 1 路分量的, 1 路 VGA 的

- D. 1路视频输出,1路重低音输出;

本机芯还有本地酷开、网络酷开功能。本地酷开有酷影、酷K和音乐相册功能; 网络酷开则在线酷影、在线酷开、下载搜索和健康运动功能。

本机芯可以通过 USB、VGA 端口和烧录工具进行软件升级和烧录。

#### 1.3 主要技术规格

- 1. 支持ISP(在系统可编程)功能,同时支持USB升级功能。

- 2. 内置32-bit RISC CPU。

- 3. 支持PAL、NTSC视频解码,内置3D梳状滤波器。

- 4. 支持各种音频处理,支持SRS功能。

- 5. 内置中频处理,降低成本。

- 6. 3D-DEINTELACE, 自动检测3: 2, 2: 2电影模式。

- 7. 3D降噪, 六基色处理, 水平方向MEMC(配合6M20, 3D-MEMC)。

- 8. LVDS输出可到10BIT, 1920×1080。

- 9. 多媒体接口USB2.0,支持音画同播,支持网上的大部分格式。

- 10. 核心供电为1.28V,整机功耗小于0.5W,封装为LFBGA536。

- 11. 支持硬盘的格式FAT32和NIFS。

- 12. 功放支持2.1声道。

- 13. 各通道最高可支持的格式如表1.1所示。

| 输入通道    | 最高可支持的格式               |

|---------|------------------------|

| TV      | PAL/NTSC               |

| AV      | PAL/NTSC               |

| YUV/VGA | 1080P/60               |

| HDMI    | HDMI1.3 1080P/60/12BIT |

|         | MPEG2 1080P/60         |

| USB     | MPEG4 1080P/60         |

| 000     | RM 720P/60             |

|         | H.264 1080P/60         |

表 1.1 各通道最高可支持的格式

# 2 电路介绍

#### 2.1、 主板与副板、扩展板的接口定义如下:

1. 主板与副板接口:

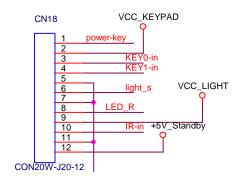

图2.1 主板与副板接口

说明:

PIN1: CPU 的 GPIO,用来做待机按键接口或者用来控制指示灯的蓝灯的亮暗。

PIN2: 键控板供电,接主板电源 standby 3.3V。

PIN3、4: 键控的2路模拟电压输入,接 CPU的 A/D 口。

PIN6: 环境光检测信号输入,为模拟电压,接 CPU的 A/D 口。

PIN8: LED 指示灯颜色切换控制,接 CPU 的 GPIO。

PIN9: 指示灯板供电,接主板电源 standby 3.3V。

PIN10: 遥控输入。

PIN12: 遥控接收板供电,接主板电源 standby 5V。

PIN5、7、11:接地。

2. 主板与卡拉 OK 板接口:

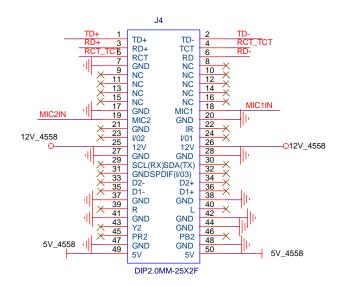

图2.2主板与卡拉 OK 板接口

#### 说明:

因为卡拉 OK 功能由6I48实现,不需要外接卡拉 OK 功能模块,所以卡拉 OK 板上只需要 MIC 接口、MIC 音频放大电路以及网口。

接口上实际用到的 PIN 脚如上图:

PIN1~6: RJ45网络信号输入。

PIN18、19: MIC 麦克风音频输入。

PIN25、26: 卡拉 OK 板12V 供电。

PIN49、50: 卡拉 OK 板5V 供电。

PIN7、17、20、27、28、37、38、41、42、47、48: 接地。

3. 主板与 MEMC 板接口:

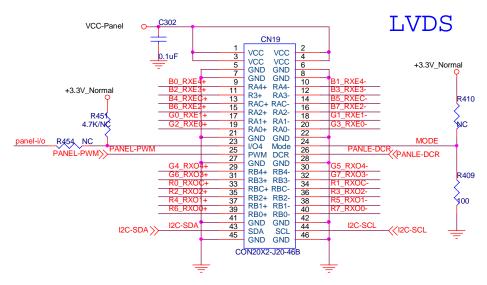

图2.3主板与 MEMC 板接口

#### 说明:

PIN1~4: MEMC 板供电,根据不同屏选择接主板12V 或者5V 电源。

PIN9~20: A组LVDS信号。

PIN23:接 CPU的 GPIO口,用来控制LG 屏的 local dimming 功能的开和关。

PIN24: 屏 TI 模式、8bit/10bit 选择信号。

PIN25: PWM 信号输出,接主板 CPU 背光控制 PWM 脚。

PIN26: 屏输出 DCR 背光控制信号。

PIN29~40: B组LVDS信号。

PIN43、44: I2C 总线,接主板 CPU 的 I2C 总线接口,用于控制 MEMC 芯片。

PIN5~8、21、22、27、28、41、42、45、46: 接地。

#### 2.2、主板与电源板接口和供电系统:

1. 主板与电源板接口:

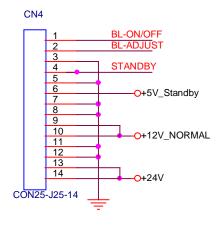

图2.4主板与电源板接口

说明:

PIN1: 背光开关控制信号。

PIN2: 背光亮度调节信号。

PIN4: 电源板待机控制信号。

PIN6: 待机5V 电源, 电源板待机状态下仍能保持供电。

PIN9、10: 12V 电源, 电源板待机状态下不供电。

PIN13、14: 24V 电源, 电源板待机状态下不供电。

PIN3、5、7、8、11、12:接地。

2. 主板供电系统:

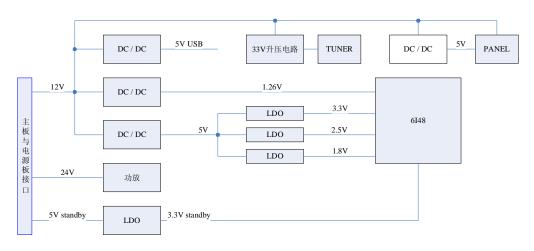

图2.5主板供电系统

各路 DC 和 LDO 的输出的电压值如表 2.1 所示

| 功能          | 位号   | 测量器件  | 理论电压值     | 说明                 |

|-------------|------|-------|-----------|--------------------|

| 主芯片核电压      | U6   | C71   | 1.20V     | 电压最高不能超过 1.3V      |

| Normal 5V   | U7   | CA103 | 5.0V      |                    |

| USB 系统供电    | U8   | D5    | 5.0V      | 电压超过 5.4 有可能烧坏硬盘   |

| Normal 3.3V | U23  | CA7   | 3.3V      |                    |

|             |      |       |           | 此电压过高或过底会导致 DDR    |

| DDR 工作电压    | U24  | CA15  | 1.8V      | PHASE 偏离造成死机, 花屏等问 |

|             |      |       |           | 题                  |

| Normal 2.5V | U27  | CA9   | 2.5V      | MST6148的 ADC部分电路供电 |

| 功放芯片供电      | U36  | R442  | 24V       | 电压异常会导致断音、无声       |

| 网口芯片供电      | U40  | CA49  | 3.3V      | 电压异常导致无法连接网络       |

| 屏、MEMC 板供   | C302 | C302  | 5V 或者 12V | 配屏不同电压不同, 12V 点 5V |

| 电           |      |       |           | 屏会烧坏屏              |

| 高频头调谐电压     |      | 33V   | 稳压管 D85 上 | 此处电压测 D3 电压太低,高频   |

|             |      |       | 电压        | 段无台。               |

表 2.1 各路 DC 和 LDO 的输出的电压值

#### 2.3 机芯部分电路

背光控制电路见 背光控制电路原理图;

#### 2.4 主要信号流程介绍

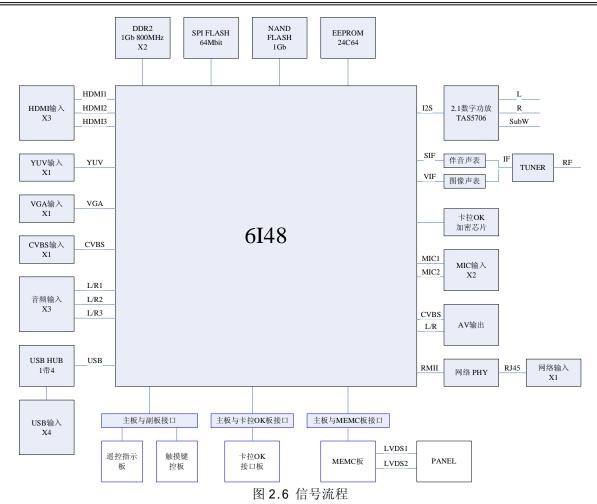

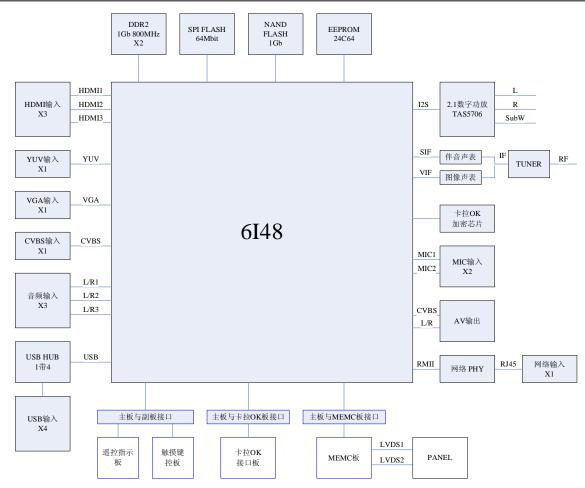

信号流程原理框图如图 2.6 所示

#### 2.5 伴音信号流程

# 3 主要芯片、主要信号流程介绍

## 3.1 主芯片(U9): 6148

# 3.11 芯片概述

6148是一个高度集成化的 IC,除了集成了 CPU、SCALER、TV DECODER 外,还包含了模拟 TV demod 和中放、音效处理 DSP、多媒体编解码、网络等众多强大的功能,同时还支持最高达4路 HDMI1.3和2路 USB2.0。高度的集成化也让整个设计变得简洁,工作流程也简单明了。

众多的视频信号从各自的接口输入6148后,经过解调、解码、ADC、画质调整、SCALER 后输出60Hz LVDS 信号,经过 MEMC 板处理转换成120Hz 双路 LVDS 信号输出给120Hz 的液晶屏。另外,视频信号经过 DAC 后,还支持 CVBS 输出。TV 内置中频解调,支持 PAL,NTSC,SECAM 视频解码,内置3D 梳状滤波器,3D 降噪,六基色处理,3D-DE INTELACE,自动检测3:2,2:2 电影模式,最高可以支持到10BIT、1920X1080、120Hz 的屏,HDMI接口支持1.3版本和 HDCP, USB 支持2.0版本。

音频信号输入6148后,经过解调、ADC、解码、DSP 音效处理、音量调节后通过 I2S 接口输出给2.1数字功放,最后输出左右声道音频到左右喇叭,同时还输出1路重低音信号到重低音接口供外接低音音箱使用。 另外,音频信号经过 DAC 后,还支持模拟左右声道立体声输出。音效支持 SRS、5段均衡器。

CPU 为32-bit MIPS 架构,主频为500M,支持 ISP(在系统可编程)功能,同时支持 USB 升级功能。另外,还内置待机控制 CPU,大大降低待机功耗,实现待机功耗低于0.5W 的绿色节能标准。

USB 接口支持 U 盘、移动硬盘等多种 USB 存储设备,通过内置强大的多媒体编解码器,能够播放 USB 存储设备上的多种视频、音频、图片、文本内容。视频播放支持1080P MPEG2,支持 VC-1、FLV、MPEG1、MPEG4 视频格式文件,H.264支持到1080P ,RMVB 支持到1080P 并支持 RV8/9/10。音频播放支持 MPGE/1、MPGE/2、MP3、AC-3、WMA、AAC、CDDA 多种数字音频格式。图片支持 JPEG、BMP、PNG。文本支持 TXT。另外,硬盘支持格式 FAT32和 NTFS。通过 USB 接口外接2.4G USB dangle、U 盘和2.4G 手柄,可以支持多种有趣的健康运动。

网络数据通过 RJ45接口输入到以太网的 PHY 芯片处理后,通过 RMII 接口输入到6148内部网络处理模块,可以实现网络连接。另外,还可以通过 USB 接口外接 USB WIFI dangle 实现无线网络连接,同时支持无线网络一键通,通过按 USB WIFI dangle 上的一个按键可以自动迅速完成无线网络相关设置。RJ45接口如果外接 ADSL MODEN,可以通过电视机直接 ADSL 拨号上网。通过网络,可以实现在线观看电影、电视剧,搜索下载视频内容。

MIC 接口外接麦克风输入的模拟音频信号通过运放放大,输入到6148,经过内置音频 ADC 后和卡拉 OK 伴奏混频后,可以实现卡拉 OK 功能。卡拉 OK 的伴奏内容经过加密后存储在 U 盘上,通过 USB 接口接入,经过解密、解码后播放并与 MIC 声音混频。另外,音频 DSP 还支持伴奏音量、MIC 音量、音调等调整。

## 3.12 芯片内部框图

图3.1 芯片6I48框架图

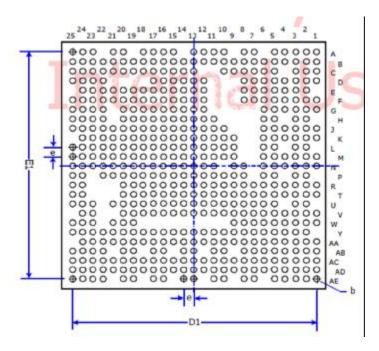

#### 3.13 芯片的管脚示意图

图3.2 芯片6148管脚示意图

#### (1)芯片6148供电要求

## Recommended Operating Power Conditions

| Parameter             | Symbol               | Min  | Тур  | Max  | Units |

|-----------------------|----------------------|------|------|------|-------|

| 3.3V Supply Voltages  | V <sub>VDD_33</sub>  | 3.14 |      | 3.46 | V     |

| 2.5V Supply Voltages  | V <sub>VDO 25</sub>  | 2.38 |      | 2.62 | ٧     |

| 1.8V Supply Voltages  | V <sub>VDO 18</sub>  | 1.70 | 2 (2 | 1.90 | V     |

| 1.26V Supply Voltages | V <sub>VDD_126</sub> | 1.20 |      | 1.32 | V     |

图3.3 芯片6148供电

#### (2)芯片复位

此芯片的复位引脚C5为高电平复位,正常时为低电平。

#### (3)MST6148芯片对E70机芯的相关信号定义:

- ① MST6I48芯片引脚 K1、M2、K3分别为VGA的R、G、B信号输入; N5为VGA-HS输入, P6 为VGA-VS输入。

- ② MST6I48芯片引脚D2和D1、引脚A2和B3、引脚G1和G2分别为HDMI0、HDMI1、HDMI2的时钟差分信号输入;引脚E2、D3、F2、E3、F3、F1为HDMI0的差分信号输入,引脚D2、A1、C2、B1、C3、C1为HDMI1的差分信号输入,引脚H2、G3、J2、H3、J3、J1为HDMI2的差分信号输入。

- ③ MST6I48芯片引脚R1为Pr信号输入、引脚U2为Pb信号输入、引脚T1、T2为Y信号输入。

- ④ MST6I48芯片引脚V2为AV1视频信号输入; MST6I48芯片引脚AA4、AB4为8M86机芯的音频输出。

- ⑤ MST6I48芯片引脚AD3、AE3为SIF音频输入。

- ⑥ MST6I48芯片引脚T5、T4为VGA伴音输入;引脚U5、U6为AV1、Y1PB1PR1伴音输入;

#### (4)12C 总线控制引脚

MST6I48芯片引脚AA22、Y22分别为SCL、SDA,系统采用这一路IIC做控制。

#### 3.2 功放 IC (U41): STA5706

#### 3.21 芯片概述

功放 IC 采用 TI 公司的纯数字攻放 TAS5706, TAS5706 的音频输入是 I<sup>2</sup>S 数字音频信号,跟模拟音频输入的攻放相比,减少了 A/D 和 D/A 的处理过程,保留了音频的原始数据。TAS5706 还内置了 DSP,可以对各路输出音频进行的高音、低音和音量调整,让声音效果最佳。本芯片还包含 4 个独立半桥输出,通过一定的配置,可以实现 2.1 音频输出。

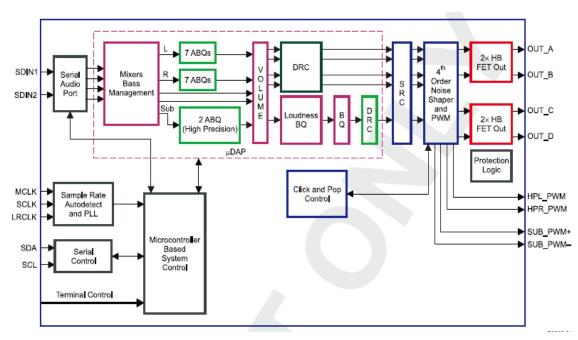

### 3.22 芯片内部框图

TAS5706芯片内部框图如图3.4所示。

图 3.4 TAS5706 内部框架示意图

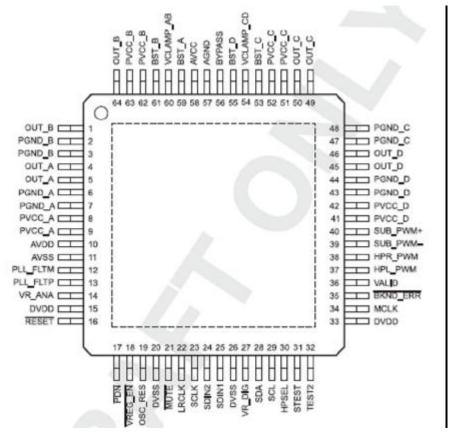

## 3.23 管脚示意如图 3.5 所示,

图 3.5 TAS5706 管脚示意图

- 3.24 管脚说明见: TAS5706 pin;

- 3.25 芯片对应的工作电压

|                    |                                                                      | VALUE              | UNIT |

|--------------------|----------------------------------------------------------------------|--------------------|------|

| Committee          | DVDD, AVDD                                                           | -0.3 to 3.6        | V    |

| Supply voltage     | PVCC                                                                 | -0.3 to 30         | V    |

|                    | ut voltage 3.3-V digital input                                       | -0.5 to DVDD + 0.5 | V    |

| Input voltage      | 5-V tolerant <sup>(2)</sup> digital input                            | -0.5 to DVDD + 2.5 | V    |

| Input clamp cum    | ent, I <sub>IK</sub> (V <sub>I</sub> < 0 or V <sub>I</sub> > 1.8 V   | ±20                | mA   |

| Output clamp ou    | rrent, I <sub>OK</sub> (V <sub>O</sub> < 0 or V <sub>O</sub> > 1.8 V | ±20                | mA   |

| Operating free-a   | r temperature                                                        | 0 to 85            | *C   |

| Operating junction | on temperature range                                                 | 0 to 150           | *C   |

| Storage tempera    | ture range, T <sub>stg</sub>                                         | -40 to 125         | °C   |

表 3.2 芯片 TAS5706 工作电压

# 3.26 芯片出现异常的故障现象

如果 TAS5706 芯片焊接不好,或者芯片损坏,会出现输出无声或者声音不正常等现象。

## 3.3 网口芯片 (U34): IP101A

## 3.31 芯片概述

IP101ALF 提供两个 10/100Mbps 快速以太网地址,支持全/半双工模式,端口基于 IEEE 802.3/802.3u,支持 MDI/MDIX 功能,用户可以能通过 MII 和 RMII 接口与外部 PHY 或以太网交换芯片构建 VOIP 网关。

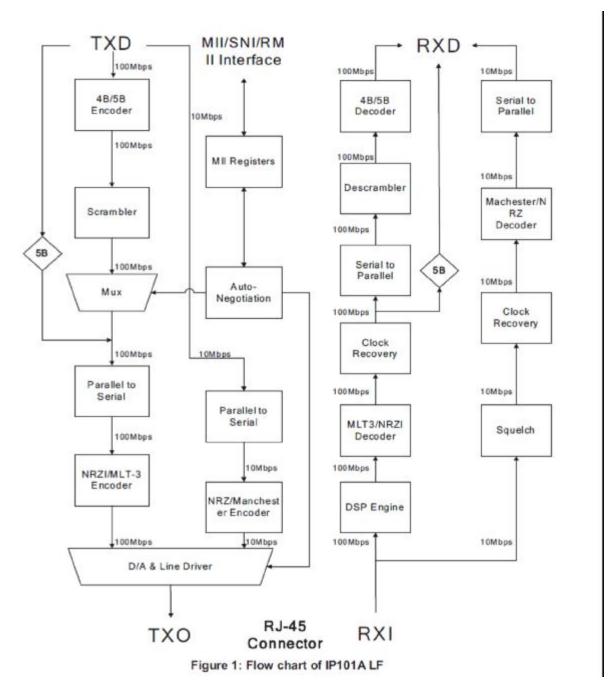

# 3.32 芯片内部框图

芯片内部框图如图 所示:

图 3.6 芯片 IP101A 内部框图

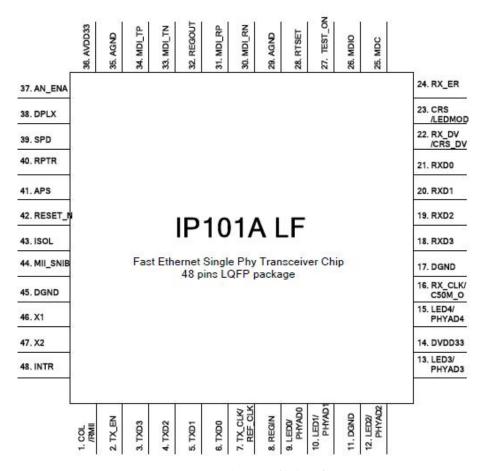

# 3.33 芯片管脚示意图

图3.7 芯片IP101A管脚示意图

#### 3.34 芯片重要管脚功能及对应工作电压

芯片管脚功能见 IP101A

#### 3.35 芯片出现异常的故障现象

IP101ALF芯片出现异常时网络不能正常访问。

## 3.4 USB HUB 芯片 (U28): GL850G

#### 3.41 芯片概述

芯片GL850G是一款USB HUB的芯片,内置一颗8位的RISC的处理器去处理USB HUB芯片四个USB口之间的管理并负责和主USB之间的通讯,支持USB2.0标准并兼容1.1标准。供电方面采用两种供电方式:1、同时采用5V和3.3V供电,这种模式下的IC的工作温度会稍微低一点;2、是外部只采用5V供电,通过IC内部的LD0把5V转换成3.3V来供电,可以节约成本。

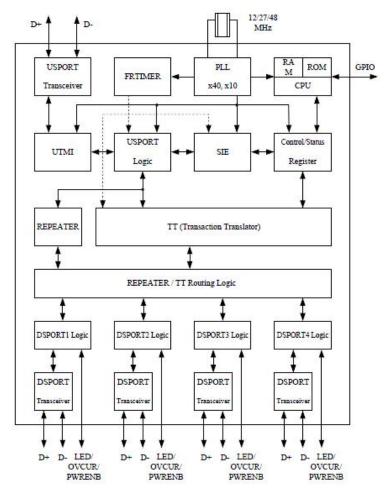

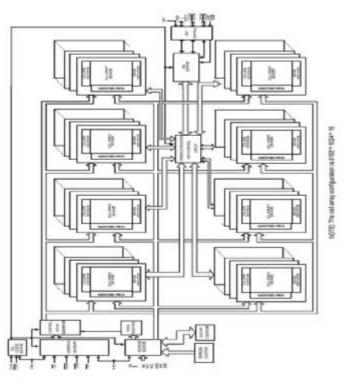

#### 3.42 芯片内部框图

图3.8 芯片GI850G内部框图

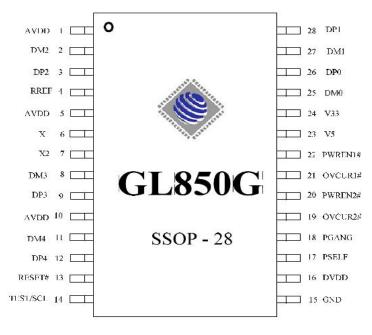

## 3.43 芯片管脚示意图

图3.9 芯片GL850G管脚示意图

# 3.44 芯片重要管脚功能及对应工作电压

芯片管脚功能见GL850G。

## 3.45 芯片出现异常的故障现象

GL850G芯片出现异常时USB设备不能正常识别或者访问。

#### 3.5 NAND FLASH芯片 (U54): K9F1G08U0C-PCB0

#### 3.5.1 芯片概述

K9F1G08U0C-PCB0芯片为128M×8Bit 的NAND Flash, 支持2.7V~3.6V的电压输入,存储单元阵列为(128M+4M)×8bit,数据寄存器为(2K+64)×8bit,芯片正常采用3.3V供电。

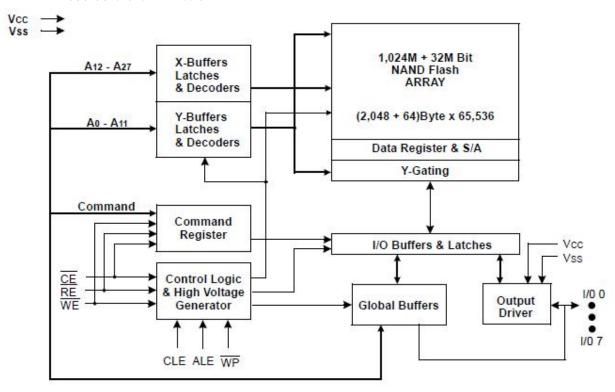

### 3.5.2 芯片内部框图

芯片内部框图如图3.10所示。

图3.10 芯片内部框图

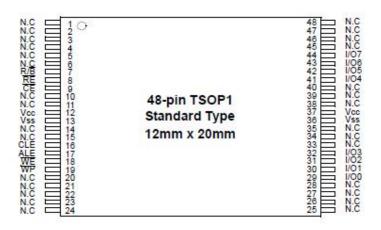

## 3.5.3 芯片管脚图

芯片管脚图如图3.11所示

#### K9F1G08X0C-PCB0/PIB0

图3.11 芯片管脚图

# 3.5.4 芯片重要管脚功能及对应工作电压

芯片管脚图和电压范围分别如图3.12和图3.13所示

#### PIN DESCRIPTION

| Pin Name  | Pin Function                                                                                                                                                                                                                                                                                                                               |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VO0 ~ VO7 | DATA INPUTS/OUTPUTS  The I/O pins are used to input command, address and data, and to output data during read operations. The I/O pins float to high-z when the chip is deselected or when the outputs are disabled.                                                                                                                       |

| CLE       | COMMAND LATCH ENABLE  The CLE input controls the activating path for commands sent to the command register. When active high, commands are latched into the command register through the I/O ports on the rising edge of the WE signal                                                                                                     |

| ALE       | ADDRESS LATCH ENABLE  The ALE input controls the activating path for address to the internal address registers. Addresses are latched on the rising edge of WE with ALE high.                                                                                                                                                              |

| CE        | CHIP ENABLE  The CE input is the device selection control. When the device is in the Busy state, CE high is ignored, and the device does not return to standby mode in program or erase operation.                                                                                                                                         |

| RE        | READ ENABLE  The RE input is the serial data-out control, and when active drives the data onto the I/O bus. Data is valid tREA after the falling edge of RE which also increments the internal column address counter by one.                                                                                                              |

| WE        | WRITE ENABLE The WE input controls writes to the I/O port. Commands, address and data are latched on the rising edge of the WE pulse.                                                                                                                                                                                                      |

| WP        | WRITE PROTECT The WP pin provides inadvertent program/erase protection during power transitions. The internal high voltage generator is reset when the WP pin is active low.                                                                                                                                                               |

| R/B       | READY/BUSY OUTPUT  The R/B output indicates the status of the device operation. When low, it indicates that a program, erase or random read operation is in process and returns to high state upon completion. It is an open drain output and does not float to high-z condition when the chip is deselected or when outputs are disabled. |

| Voc       | POWER Vox is the power supply for device.                                                                                                                                                                                                                                                                                                  |

| Vss       | GROUND                                                                                                                                                                                                                                                                                                                                     |

| N.C       | NO CONNECTION Lead is not internally connected.                                                                                                                                                                                                                                                                                            |

Note: Connect all Vcc and Vss pins of each device to common power supply outputs.

Do not leave Vcc or Vss disconnected.

图3.12 芯片管脚图

#### RECOMMENDED OPERATING CONDITIONS

(Voltage reference to GND, K9F1G08X0C-PCB0 :TA=0 to 70°C, K9F1G08X0C-PIB0:TA=-40 to 85°C)

| Danamatan      | Cumbal | K9  | F1G08B0C(2 | 2.7V) K9 |     | F1G08U0C(3 | Unit |   |

|----------------|--------|-----|------------|----------|-----|------------|------|---|

| Parameter      | Symbol | Min | Тур.       | Max      | Min | Тур.       | Max  |   |

| Supply Voltage | Vcc    | 2.5 | 2.7        | 2.9      | 2.7 | 3.3        | 3.6  | V |

| Supply Voltage | Vss    | 0   | 0          | 0        | 0   | 0          | 0    | V |

图3.13 芯片K9F1G08U0C-PCB0 工作电压示意图

## 3.5.5 芯片出现异常的故障现象

芯片出现故障时机器工作出现异常,比如NAND FLASH 物理损害,或NAND FLASH中的程序数据被破坏,都会导致机器无法正常运行,出现通道无信号、黑屏等现象。

## 3.6 SPI FLASH芯片 (U44): EN25F16-100HIP

## 3.61 芯片概述

型号为EN25F16-100HIP的芯片是EON公司生产的串行FLASH,容量为16Mbit,供电电压范围为2.7V-3.6V,串行输入输出,有软/硬件的写保护功能。

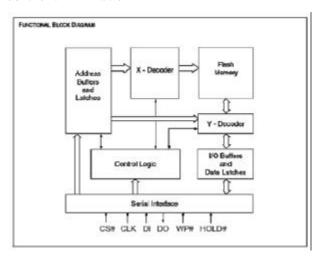

### 3.62 芯片内部框图

EN25F16-100HIP芯片的内部框图如图3.14 所示

图3.14 EN25F16-100HIP的内部框图

### 3.63 芯片管脚示意图

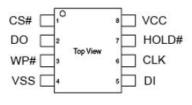

EN25F16-100HIP芯片的管脚示意图3.15

8 - LEAD SOP / DIP

图3.15 EN25F16-100HIP芯片的管脚

EN25F16-100HIP芯片的管脚功能示意图3.16

| Symbol | Pin Name                  |

|--------|---------------------------|

| CLK    | Serial Clock Input        |

| DI     | Serial Data Input         |

| DO     | Serial Data Output        |

| CS#    | Chip Enable               |

| WP#    | Write Protect             |

| HOLD#  | Hold Input                |

| Voc    | Supply Voltage (2.7-3.6V) |

| Vss    | Ground                    |

图3.16 EN25F16-100HIP芯片的管脚功示意图

其中SI/SI00为数据输入管脚,包括写入指令,数据,地址信息等;SO/SI01为数据输出管脚,主要是从设备中读出数据;SCLK为时钟控制管脚,主要是为数据的输出、输入提供时间选择,WP为写保护控制脚,当接地时,写保护。

## 3.64 芯片出现异常的故障现象

当MX25L6405DMI-12G虚焊或损坏时,会出现程序烧录不正常等现象。

3.7 DDR芯片(U12、U13): W971GG6JB-18

## 3.71 芯片概述

E70机芯采用的是WINBOND公司型号为W971GG6JB-18,容量为1G bits的DDR2 SDRAM (Double Data Rate SDRAM的缩写,双倍速率同步动态随机存储器),系统开机后,主IC MST6I48先将主程序装载到DDR2 SDRAM 中,然后才开始主程序的运行。

## 3.72 芯片内部框架

芯片内部框架如图3.17所示:

图3.17 芯片W971GG6JB-18内部框架图

# 3.73 芯片管脚图

芯片管脚图如图3.18 所示

| 1    | 2          | 3          | 4 | 5 | 6 | 7     | 8    | 9    |

|------|------------|------------|---|---|---|-------|------|------|

| VDD  | NC         | VSS        |   | Α |   | VSSQ  | UDQS | VDDQ |

| DQ14 | VSSQ       | UDM        |   | В |   | UDQS  | VSSQ | DQ15 |

| VDDQ | DQ9        | VDDQ       |   | С |   | VDDQ  | DQ8  | VDDQ |

| DQ12 | VSSQ       | DQ11       |   | D |   | DQ10  | VSSQ | DQ13 |

| VDD  | NC         | VSS        |   | E |   | VSSQ  | LDQS | VDDQ |

| DQ6  | VSSQ       | LDM        |   | F |   | LDQS  | VSSQ | DQ7  |

| VDDQ | DQ1        | VDDQ       |   | G |   | VDDQ  | DQo  | VDDQ |

| DQ4  | VSSQ       | DQ3        |   | Н |   | DQ2   | VSSQ | DQ5  |

| VDDL | VREF       | VSS        |   | J |   | VSSDL | CLK  | VDD  |

|      | CKE        | WE         |   | K |   | RAS   | CLK  | ODT  |

| BA2  | BAO        | BA1        |   | L |   | CAS   | CS   |      |

|      | A10/AP     | A1         |   | M |   | A2    | Ao   | VDD  |

| VSS  | Аз         | <b>A</b> 5 |   | N |   | A6    | A4   |      |

| ři.  | <b>A</b> 7 | A9         |   | Р |   | A11   | A8   | VSS  |

| VDD  | A12        | NC         |   | R |   | NC    | NC   |      |

图3.19芯片W971GG6JB-18管脚示意图

# 3.74 芯片重要引脚功能及对应工作电压

芯片引脚功能如表3.2 所示

| BALL NUMBER                                             | SYMBOL          | FUNCTION                      | DESCRIPTION                                                                                                                                                                                                                                                                                                                         |

|---------------------------------------------------------|-----------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M8,M3,M7,N2,N8,N3<br>,N7,P2,P8,P3,M2,P7<br>,R2          | A0-A12          | Address                       | Provide the row address for active commands, and the column<br>address and Auto-precharge bit for Read/Write commands to select<br>one location out of the memory array in the respective bank.<br>Row address: A0-A12.                                                                                                             |

|                                                         |                 | 35                            | Column address; A0-A9. (A10 is used for Auto-precharge)                                                                                                                                                                                                                                                                             |

| L2,L3,L1                                                | BA0-BA2         | Bank Select                   | BA0-BA2 define to which bank an ACTIVE, READ, WRITE or<br>PRECHARGE command is being applied.                                                                                                                                                                                                                                       |

| G8,G2,H7,H3,H1,H9<br>,F1,F9,C8,C2,D7,D3,<br>D1,D9,B1,B9 | DQ0-DQ15        | Data Input<br>/ Output        | Bi-directional data bus.                                                                                                                                                                                                                                                                                                            |

| К9                                                      | ODT             | On Die Termination<br>Control | ODT (registered HIGH) enables termination resistance internal to the<br>DDR2 SDRAM.                                                                                                                                                                                                                                                 |

| F7,E8                                                   | LDQS,           | LOW Data Strobe               | Data Strobe for Lower Byte: Output with read data, input with write data for source synchronous operation. Edge-aligned with read data, center-aligned with write data. LDQS corresponds to the data on DQ0-DQ7. LDQS is only used when differential data strobe mode is enabled via the control bit at EMR (1)[A10 EMRS command].  |

| B7,A8                                                   | UDQS,<br>UDQS   | UP Data Strobe                | Data Strobe for Upper Byte: Output with read data, input with write data for source synchronous operation. Edge-aligned with read data, center-aligned with write data. UDQS corresponds to the data on DQS-DQ15. UDQS is only used when differential data strobe mode is enabled via the control bit at EMR (1)[A10 EMRS command]. |

| L8                                                      | <del>cs</del>   | Chip Select                   | All commands are masked when $\overline{CS}$ is registered<br>HIGH. $\overline{CS}$ provides for external bank selection on systems with<br>multiple ranks. $\overline{CS}$ is considered part of the command code.                                                                                                                 |

| K7,L7,K3                                                | RAS, CAS,<br>WE | Command Inputs                | RAS, CAS and WE (along with CS) define the command being entered.                                                                                                                                                                                                                                                                   |

| B3,F3                                                   | UDM<br>LDM      | Input Data Mask               | DM is an input mask signal for write data. Input data is masked when DM is sampled high coincident with that input data during a Write access. DM is sampled on both edgas of DQS. Although DM pins are input only, the DM loading matches the DQ and DQS loading.                                                                  |

| J8,K8                                                   | CLK,<br>CLK     | Differential Clock<br>Inputs  | CLK and CLK are differential clock inputs. All address and control input signals are sampled on the crossing of the positive edge of CLK and negative edge of CLK. Output (read) data is referenced to the crossings of CLK and CLK (both directions of crossing).                                                                  |

| К2                                                      | CKE             | Clock Enable                  | CKE (registered HIGH) activates and CKE (registered LOW) deactivates clocking circuitry on the DDR2 SDRAM.                                                                                                                                                                                                                          |

| J2                                                      | VREF            | Reference Voltage             | VREF is reference voltage for inputs.                                                                                                                                                                                                                                                                                               |

| A1,E1,J9,M9,R1                                          | VDD             | Power Supply                  | Power Supply: 1.8V ± 0.1V.                                                                                                                                                                                                                                                                                                          |

| A3,E3,J3,N1,P9                                          | VSS             | Ground                        | Ground.                                                                                                                                                                                                                                                                                                                             |

| A9,C1,C3,C7,C9,E9,<br>G1,G3,G7,G9                       | VDDQ            | DQ Power Supply               | DQ Power Supply: 1.8V ± 0.1V.                                                                                                                                                                                                                                                                                                       |

| A7,82,88,D2,D8,E7,<br>F2,F8,H2,H8                       | VSSQ            | DQ Ground                     | DQ Ground. Isolated on the device for improved noise immunity.                                                                                                                                                                                                                                                                      |

| A2,E2,L1,R3,R7,R8                                       | NC              | No Connection                 | No connection                                                                                                                                                                                                                                                                                                                       |

| .J7                                                     | VSSDL           | DLL Ground                    | DLL Ground.                                                                                                                                                                                                                                                                                                                         |

| J1                                                      | VDDL            | DLL Power Supply              | DLL Power Supply: 1.8V ± 0.1V.                                                                                                                                                                                                                                                                                                      |

表3.2 芯片W971GG6JB-18管脚功能表

工作电压为1.8V,如图3.19所示,具体请参考原理图

| SYM. | PARAMETER                    | MIN.        | TYP.       | MAX.        | UNIT | NOTES |

|------|------------------------------|-------------|------------|-------------|------|-------|

| Vpp  | Supply Voltage               | 1.7         | 1.8        | 1.9         | V    | 1     |

| VDDL | Supply Voltage for DLL       | 1.7         | 1.8        | 1.9         | V    | 5     |

| VDDQ | Supply Voltage for Output    | 1.7         | 1.8        | 1.9         | V    | 1,5   |

| VREF | Input Reference Voltage      | 0.49 x VDDO | 0.5 x V000 | 0.51 x VDDQ | V    | 2,3   |

| VTT  | Termination Voltage (System) | VREF - 0.04 | VREF       | VREF + 0.04 | V    | 4     |

#### Notes:

- There is no specific device VDD supply voltage requirement for SSTL\_18 compliance. However under all conditions VDDQ must than or equal to VDD.

- The value of VREF may be selected by the user to provide optimum noise margin in the system. Typically the value of VREF is expected to be about 0.5 x VDDQ of the transmitting device and VREF is expected to track variations in VDDQ.

- 3. Peak to peak AC noise on VREF may not exceed 4/-2 % VREF(dc).

- 4. VTT of transmitting device must track VREF of receiving device.

- 5. VDDQ tracks with VDD, VDDL tracks with VDD. AC parameters are measured with VDD, VDDQ and VDDDL field together.

图3.19芯片W971GG6JB-18工作电压

# 3.75 芯片出现异常的故障现象

如果主IC与DDR2 SDRAM之间的匹配电阻虚焊,或者DDR引脚虚焊,芯片出现故障时,则会出现系统启动不了的现象,表现为无信号输出;而且从打印信息中可以获得提示:正常状态下的打印信息如图 所示

UART\_115200 BISTO-OK BIST1-OK

如果DDR出现异常的话,则会出现BISTO-Fail的提示信息。

## 3.8 卡拉OK解密芯片(U37): MK-900 MULTAK

# 3.81 芯片概述

芯片MK-900内置

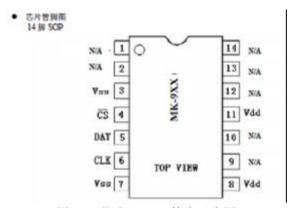

# 3.82 芯片管脚

图3.20 芯片MK-900管脚示意图

# 3.83 芯片管脚功能和工作电压说明

| 200     |           | 100 |         |                      |

|---------|-----------|-----|---------|----------------------|

| 323,900 |           | -   |         |                      |

| 1       | P1.0/ADC1 | 1/0 | TTL SMT | 双向输入输出端口, ADC 模拟信号输入 |

| 2       | N/A       |     | N/A     | N/A                  |

| 3       | Vss       | P   | -       | 地, 0V 参考点            |

| 4       | /CS       | 1   | TTL SMT | 单向输入端口               |

| 5       | DAT       | I/O | TTL SMT | 双向输入输出端口,数据通信端口      |

| 6       | CLK       | I   | TTL SMT | 单向输入端口, 时钟通信端口       |

| 7       | Vss       | P   | -       | 地, 0V参考点。            |

| 8       | Vdd       | P   | -       | 电源                   |

| 9       | N/A       |     | -       | N/A                  |

| 10      | N/A       |     | N/A     | N/A                  |

| 11      | Vdd       | P   | -       | 电源                   |

| 12      | N/A       |     | N/A     | N/A                  |

| 13      | N/A       |     | N/A     | N/A                  |

| 14      | N/A       |     | N/A     | N/A                  |

图3.21 芯片MK-900管脚功能

| 1 <b>2 3</b> 1 |                 | 4.65             |                              |    |

|----------------|-----------------|------------------|------------------------------|----|

| 电源电压           | Vpp             | _                | -0.3 ~ 7.5                   | V  |

| 输入电压           | V <sub>IN</sub> | -                | -0.3 ~ V <sub>DD</sub> + 0.3 | V  |

| 输出电压           | Vout            | _                | -0.3 ~ Vpp+0.3               | V  |

| 输出电流 (每个引脚)    | I <sub>o</sub>  | -                | 35                           | mA |

| 存储温度           | Tstg            | _                | -55~125                      | C  |

| 操作温度           | Topr            | Vpp = 3.5 ~ 5.5V | -40 ~ 85                     | τ  |

#### 图3.21芯片MK-900工作电压

# 3.84 芯片出现异常的故障现象

当芯片MK-900出现焊接异常或损坏时,卡拉OK会出现异常。

## 3.9 高频调谐器(U22):

## 3.91 高频头概述

E70机芯有两种结构,因此分为8M67和8M70两种机芯,分别采用旭光公司生产的高频调谐器是HFT-8F/115CW和HFT-8B1/V116CW。两者的本振频率是38MHz,引脚定义是兼容的,但是结构不一样。

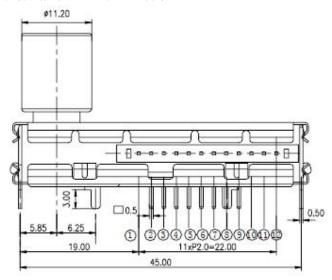

## 3.92 高频头的结构示意图

高频头的结构示意图分别如图3.22和图3.23所示

图3.22 HFT-8F/115CW 结构示意图

图3.23 HFT-8B1/V116CW 结构示意图

## 3.92 高频头管脚图

高频头管脚如图3.24所示:

| PIN | SYMBOL   |

|-----|----------|

| 1   |          |

| 2   | IF OUT   |

| 3   | VT +33V  |

| 4   | AS       |

| 5   | SDA      |

| 6   | SCL      |

| 7   | MB +5V   |

| 8   | BT(Test) |

| 9   | AGC      |

| 10  |          |

| 11  |          |

| 12  |          |

图3.24 高频头管脚示意图

高频头工作电压说明如图3.25所示:

| T        | Supply voltage |       |      |      |

|----------|----------------|-------|------|------|

| Terminal | Min.           | Тур.  | Max. | Unit |

| MB (+5V) | 4.9            | 5.0   | 5. 1 | ٧    |

| VT       | 31.0           | 33. 0 | 35.0 |      |

图3.25 高频头工作电压

# 4.0 机芯所使用的DC/DC芯片(U6、U7、U8): MP1482DS

# 4.01 芯片概述

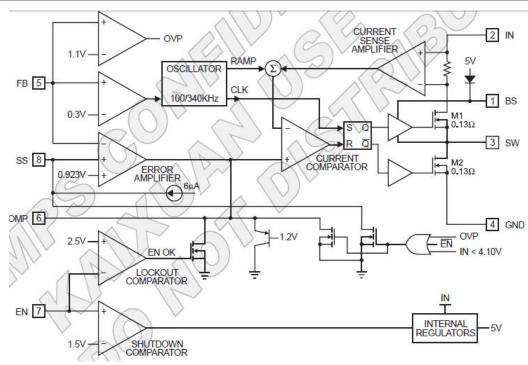

E70机芯的DC/DC芯片采用的是MPS公司的MP1482DS,完成12V转5V和12V转1.26V,是BUCK式压降的DC/DC转换器,采用同步整流方式,最高可输出2A的电流,输入电压范围为4.75V~18V,输出电压范围为0.923V~15V。

# 4.02 芯片内部框图

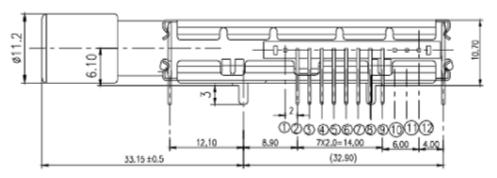

MP1482DS芯片内部框图如图3.26所示:

图3.26 芯片MP1482DS内部框图

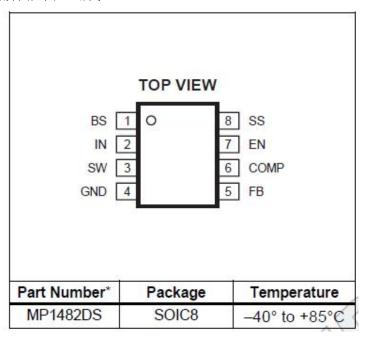

# 4.03 芯片管脚图

MP1482DS芯片管脚图如图3.27所示

图3.27 芯片MP1482DS管脚示意图

# 4.04 芯片重要引脚功能及对应工作电压

MP1482DS芯片引脚功能描述如图3.28所示

#### **PIN FUNCTIONS**

| Pin# | Name | Description                                                                                                                                                                                                                                                          |  |  |  |

|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1    | BS   | High-Side Gate Drive Boost Input. BS supplies the drive for the high-side N-Channel MOSFET switch. Connect a 0.01µF or greater capacitor from SW to BS to power the high side switch.                                                                                |  |  |  |

| 2    | IN   | Power Input. IN supplies the power to the IC, as well as the step-down converter switches. Drive IN with a 4.75V to 18V power source. Bypass IN to GND with a suitably large capacitor to eliminate noise on the input to the IC. See <i>Input Capacitor</i> .       |  |  |  |

| 3    | SW   | Power Switching Output. SW is the switching node that supplies power to the output. Connect the output LC filter from SW to the output load. Note that a capacitor is required from SW to BS to power the high-side switch.                                          |  |  |  |

| 4    | GND  | Ground:                                                                                                                                                                                                                                                              |  |  |  |

| 5    | FB   | Feedback Input. FB senses the output voltage to regulate that voltage. Drive FB with a resistive voltage divider from the output voltage. The feedback threshold is 0.923V. See Setting the Output Voltage.                                                          |  |  |  |

| 6    | COMP | Compensation Node. COMP is used to compensate the regulation control loop. Connect a series RC network from COMP to GND to compensate the regulation control loop. In some cases, an additional capacitor from COMP to GND is required. See Compensation Components. |  |  |  |

| 1    | EN   | Enable Input. EN is a digital input that turns the regulator on or off. Drive EN high to turn on the regulator, drive it low to turn it off. Pull up with 100kΩ resistor for automatic startup.                                                                      |  |  |  |

| 8    | ss   | Soft-Start Control Input. SS controls the soft start period. Connect a capacitor from SS to GND to set the soft-start period. A 0.1µF capacitor sets the soft-start period to 15ms. To disable the soft-start feature, leave SS unconnected.                         |  |  |  |

图3.28 芯片MP1482DS管脚功能说明

其中,第一引脚BS为电位拉高脚位;在BS与SW之间加一10nF的电容;第二引脚IN为输入电压供应脚位;第三引脚SW为开关输出脚位;第四引脚GND为地电平;第五引脚FB为反馈输入端;第六引脚COMP为控制电路补偿脚位;第七引脚EN为IC使能输入端,当为高电平时IC正常工作,当为低电平时IC关断不工作;第八引脚SS为软启动脚,当悬空时,IC不能软启动,当通过电容连接到地时IC可以软启动。

# 4.05 芯片出现异常的故障现象

芯片出现异常或者焊接不好时会出现无电压输出或输出电压异常等现象

### 5 PCB 顶/底层丝印

### 5.1 主板顶/底层丝印图

主板顶/底层丝印图请参考 顶层丝印;

## 5.2 副板顶/底层丝印图

主板顶/底层丝印图请参考 底层丝印;

## 6 调试说明。

E70机芯的调试说明详见调试说明

## 7 维修说明

#### 7.1 常见故障分析与注意事项

维修前先检查整个不良板有没有虚焊现象,有没有坏的器件,有没有烧坏器件,然后根据不同的现象进行相应的维修。

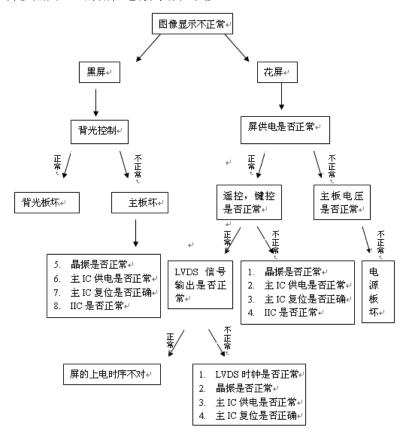

1、屏幕显示异常的情况,如果有相应的串口通讯工具和软件的话,可以通过串口的输出信息来判断软件是否正常运行,并参照图 7-1 的流程进行判断和维修:

图 7-1 屏显示异常的维修流程

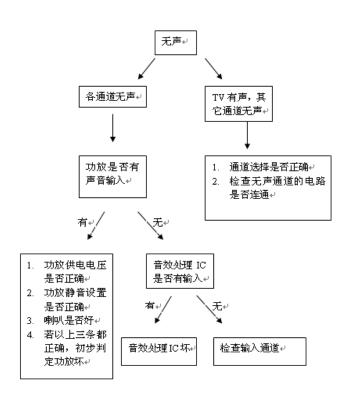

2、电视伴音异常的判断和维修流程,参考图 7-2 的流程进行判断和维修:

图 7-2 系统声音异常的判断和维修流程

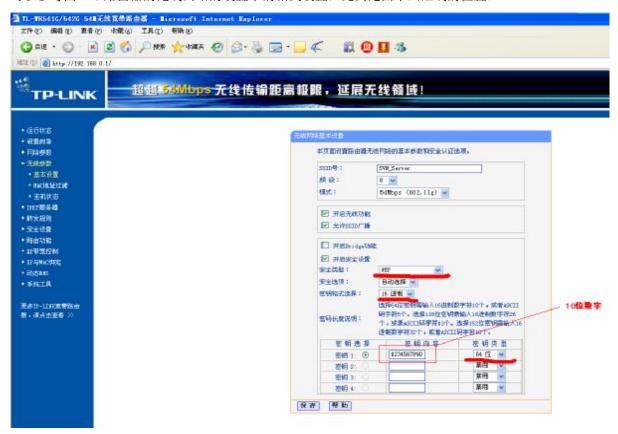

3、通过路由器无线上网无法正常连接:

如果电视通过路由器链接无法实现上网功能的时候,一般需要检查一下路由器中无线连接的设置,可以参考图 7-3 路由器的无线网络的设置中的相关设置,尤其是图中画红线的位置:

图 7-3 路由器的无线网络的设置

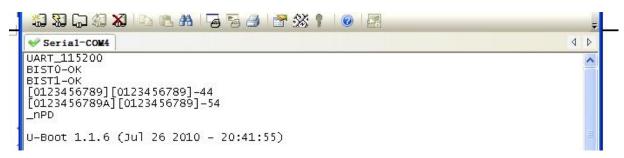

4、系统上电后发现只出现开机 LOGO 或者是屏亮的现象:

出现这种现象,在更换 U44 和 U54 的程序后该现象还是没有消失,则需要通过打印信息做进一步的判断。如图 7-3 是 BGA 焊接正常时的打印信息,系统上电后,会返回前 5 行的打印信息,如果正常的话,会显示下图所示信息,则可认为 BGA 焊接正常,否则就是 BGA 异常。其中: BISTO、BIST1 分别对应着 PCB 板上的元器件 U12、U13。

图 7-3 BGA 焊接正常时的打印信息

- 5、在工厂菜单做了些操作后,会引起系统不停的重新启动的故障 在工厂菜单中,有3个地方不要操作,否则会引起开机系统反复重启现象。这3个地方分别是:

- Ø "图像相关"——>"图像模式"——>"模式"

- Ø "图像相关"——>"白平衡"——>"模式"

- Ø "非标"——>"VD SETTING"——>"模式"

如果有被误操作导致反复重启的,可以更换 EEPROM 解决。

6、健康运动部分的说明见"健康运动说明"